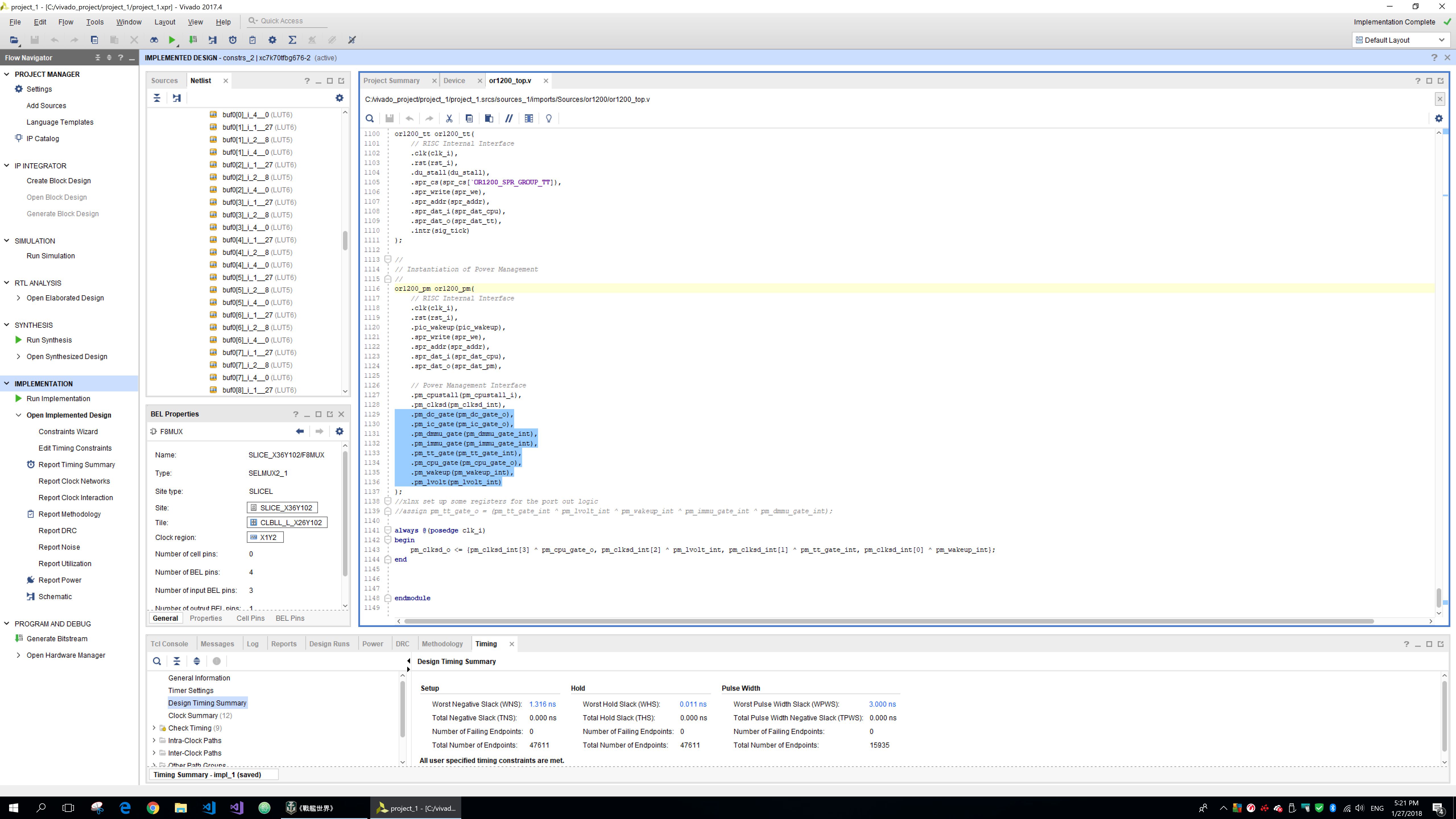

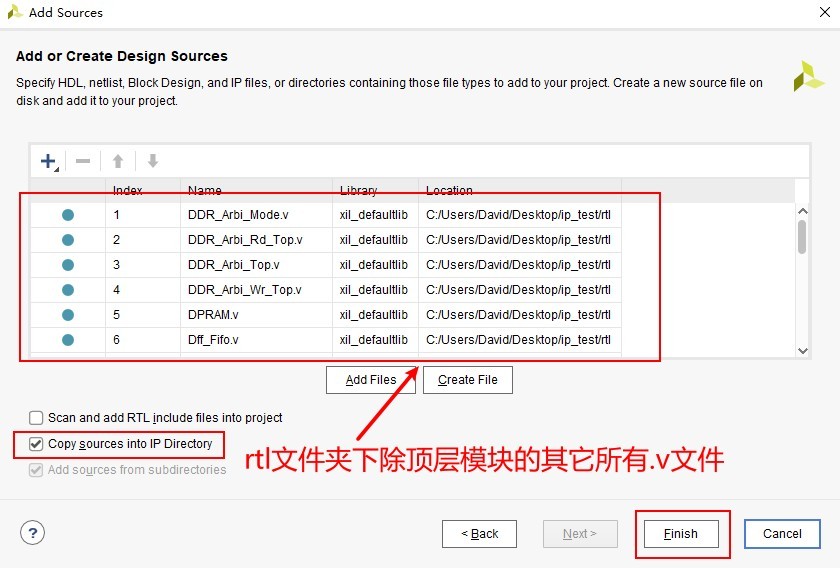

Since IPI uses IPs based on AXI protocol, you are highly encouraged to use AXI interfaces for your HLS designs, allowing the HLS IP to easily be integrated into your FPGA RTL design using the IP integration environment. It would typically take more effort to add the HLS IP into the chip-level RTL design manually (connecting each port in a text editor), than using IPI. The most productive methodology for using the outputs of HLS is the one which uses an IP integration fl ow where the RTL output from HLS is another IP block in the RTL system along with existing RTL IP.Īn IP integration environment allows the IP blocks, including the HLS-generated RTL design, to be easily integrated into the chip-level design, and is explained in Chap. The HLS output is provided in industry standard RTL format (Verilog and VHDL) and in gate-level format ( EDIF ). The output from HLS is used as RTL input to the remainder of the FPGA design fl ow.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed